文章编号: 1001-9014(2022)04-0668-04

DOI: 10. 11972/j. issn. 1001-9014. 2022. 04. 002

# Lateral linear mode avalanche photodiode through 0.35 $\mu m$ high voltage CMOS process

JU Guo-Hao<sup>1,2,3</sup>, CHENG Zheng-Xi<sup>1\*</sup>, CHEN Yong-Ping<sup>1,4\*</sup>

- (1. Shanghai Institute of Technical Physics, Chinese Academy of Sciences, Shanghai 200083, China;

- 2. University of Chinese Academy of Sciences, Beijing 100049, China;

- School of Information Science and Technology, ShanghaiTech University, Shanghai 201210, China;

Nantong Academy of Intelligent Sensing, Nantong 226000, China)

Abstract: This letter reports on a lateral linear mode avalanche photodiode through 0.35  $\mu$ m high voltage CMOS process. The linear mode avalanche photodiode is designed and fabricated with the lateral separate absorption, charge and multiplication (SACM) structure using an epitaxial wafer. The DNTUB layer, DPTUB layer, Pi layer and SPTUB layer are used for the lateral SACM structure. This improves freedom of the design and fabrication for monolithic integrated avalanche photodiode without high voltage CMOS process modifications. The breakdown voltage for the lateral linear mode avalanche photodiode is about 114.7 V. The dark currents at gain M=10 and M=50 are about 15 nA and 66 nA, respectively. The effective responsive wavelength range is  $450 \sim 1050$  nm. And the peak responsive wavelength is about 775 nm at 20 V while M=1. With unity gain (M=1), the responsivity at 532 nm is about half of the maximum.

**Key words:** avalanche photodiode, lateral SACM, high voltage CMOS, breakdown voltage **PACS:** 61. 72. uf, 85. 60. Bt, 85. 60. Dw

# 基于 0.35 μm 高压 CMOS 工艺的横向线性雪崩光电二极管

鞠国豪<sup>1,2,3</sup>, 程正喜<sup>1\*</sup>, 陈永平<sup>1,4\*</sup>

- (1. 中国科学院上海技术物理研究所,上海 200083;

- 2. 中国科学院大学,北京 100049;

- 3. 上海科技大学信息科学与技术学院,上海 201210;

- 4. 南通智能感知研究院,江苏 南通 226000)

摘要:提出了一种基于 $0.35~\mu$ m 高压 CMOS 工艺的线性雪崩光电二极管(Avalanche Photodiode, APD)。APD采用了横向分布的吸收区-电荷区-倍增区分离(Separate Absorption, Charge and Multiplication, SACM)的结构设计。横向 SACM 结构采用了高压 CMOS 工艺层中的 DNTUB层、DPTUB层、Pi 层和 SPTUB层,并不需要任何工艺修改,这极大的提高了 APD单片集成设计和制造的自由度。测试结果表明,横向 SACM 线性 APD 的击穿电压约为 114.7~V。在增益  $M=10~\pi~M=50~$ 时,暗电流分别约为  $15~\mathrm{nA}~\pi~66~\mathrm{nA}$ 。有效响应波长范围为  $450~\pi~1050~\mathrm{nm}$ 。当反向偏置电压为 20~V,即  $M=1~\mathrm{th}$ ,峰值响应波长约为  $775~\mathrm{nm}$ 。当单位增益  $(M=1)~\mathrm{th}$  ,在  $532~\mathrm{th}$  nm 处的响应度约为最大值的一半。

关键词:雪崩光电二极管;横向SACM;高压CMOS工艺;击穿电压

中图分类号:TN364 文献标识码:A

#### Introduction

radiation ( $\lambda$  < 1100 nm) has been focused on various developments of silicon avalanche photodiodes (APDs).

Optical detection of visible and near-infrared (NIR)

Received date: 2021-10-21, revised date: 2022-05-25

收稿日期:2021-10-21,修回日期:2022-05-25

Foundation items: Supported by the Shanghai Pujiang Program (18PJ1410700), Key Laboratory of Defense Technology Funding of Chinese Academy of Sciences (CXJJ-20S004), and Innovation Program of Shanghai Institute of Technical Physics, Chinese Academy of Sciences (CX-268)

Biography: JU Guo-Hao (1989-), male, Linyi China, Ph. D. Research area involves APD design and TCAD simulation. E-mail: jugh@shanghaitech. edu. cn \*Corresponding author: E-mail: chen\_yp@mail. sitp. ac. cn, czx@mail. sitp. ac. cn

APD is a semiconductor photodetector in which a photon carrier can be generated due to photoelectric effect of solid-state semiconductor material [1]. The avalanche multiplication of carriers can be triggered by the photon-generated carrier in strong electric field due to an impact-ionization mechanism [2]. The separate absorption, charge and multiplication (SACM) silicon APD [3-4] is a very attractive device with an internal avalanche gain for supporting high sensitivity and low illumination detection. It is also highly desirable to fabricate silicon APDs together with electronic circuits in a cost-effective and less-parasitic single-chip [5-6] through high voltage CMOS process without process modifications.

However, with the limitations of design rules for most CMOS process, it is extremely difficult to achieve a suitable charge layer which is used to modulate the electric field in multiplication region for the vertical SACM APDs. Until now, most commercial SACM APDs have not been able to meet the requirements of low-cost, highperformance, monolithic integration and large-scale arrays. And only units APD or small-scale linear array APD can be fabricated and available. In order to design and fabricate vertical SACM APD through CMOS process without any process modification there are two design approaches which are usually carried out to get a suitable charge layer. The first way is the transverse space doping modulation. The groups have designed several silicon APDs by applying lateral well modulation<sup>[7-8]</sup>. The other method is the compensation doping modulation. Some silicon APDs were designed by combining different doping process layers [9]. For most lateral structure silicon AP-Ds, the ordinary lateral p-n junction is adopted with p type and n type doping[10-12]

In this letter, we report the fabrication and characterization of lateral linear mode avalanche photodiode based on 0.35 µm high voltage CMOS process without any technology rules modification. This linear mode APD is fabricated with the lateral SACM structure using the 15 µm thick epitaxial layer. The photosensitive surface is an octagonal region<sup>[13]</sup> which is partially covered with electrode metal and shielding metal. In the next section, the structure and fabrication of the APD will be introduced. Then, in Sect. 2, the APD will be characterized and discussed, including current, gain, breakdown voltage and responsivity. In Sect. 3, the conclusion of this work is given.

### 1 Device structure and fabrication

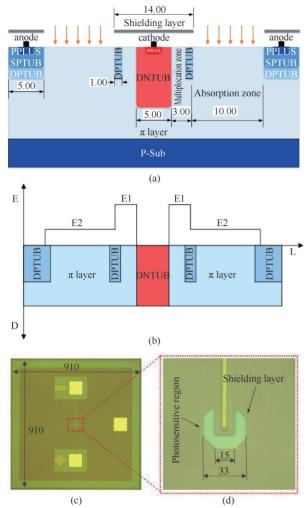

The cutaway schematic (not to scale) of the lateral SACM APD presented in this paper is seen from Fig. 1 (a). As shown in Fig. 1 (a), the linear mode APD is designed with lateral SACM structure including DNTUB (Deep-N-TUB) layer, DPTUB (Deep-P-TUB) layer, Pi  $(\pi)$  layer and SPTUB (Shallow-P-TUB) layer. The regular DNTUB layer and DPTUB layer for modulating electric field distribution are fabricated in 0. 35  $\mu m$  high voltage CMOS technology. The multiplication zone of such structure is between the central DNTUB layer and loop-locked DPTUB layer. As shown in Fig. 1 (b), this structure

ture can ensure that the lateral electric field strength in absorption zone is much lower than that in the multiplication zone, thus to confine the avalanche to the multiplication zone. The high doping concentration of the top NPLUS layer and PPLUS layer can form ohmic contact with the front metal electrodes. Meanwhile, the top NPLUS layer and PPLUS layer supply voltage to the DNTUB layer and Pi layer. The SPTUB layer and DPTUB layer connected to the PPLUS layer serve as the transition layer. Except for the absorption zone surface, the other surfaces are covered with a separate metal layer to shield incident light. The shielded multiplication zone can effectively reduce the participation of holes generated from incident light absorption in avalanche process.

Figures 1 (c) and (d) are the microscopic picture of the complete lateral SACM APD device and the microscopic picture of the photosensitive region, respectively. The size of the complete APD device is 910  $\mu m \times 910$   $\mu m$ . Excluding the center electrode, the area of the active octagonal photosensitive region is 618  $\mu m^2$ . The size of the PAD is 100  $\mu m \times 100$   $\mu m$ . The metal M3 layer and M4 layer are used as shielding layer and the top electrode, respectively.

#### 2 Results and discussions

#### 2. 1 Current and gain

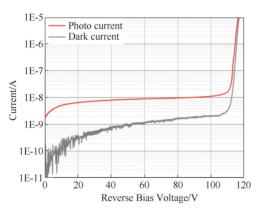

The light current and dark current of the lateral APD are measured through Keithley 4200A-SCS Parameter Analyzer. The unity gain for M=1 is defined at the low reverse bias voltage of 20 V. Furthermore, the breakdown voltage of the lateral APD is defined as the reverse voltages at which the dark current reaches 1  $\mu$ A<sup>[14]</sup>. The photocurrent is measured using a light source with center wavelength  $\lambda=905$  nm and spectral width  $\Delta\lambda=3$  nm. The dark current in Fig. 2 shows that the breakdown voltage of the lateral linear mode APD is at about 114.7 V. The dark currents of the lateral APD are about 15 nA and 66 nA when the typical gains are set at M=10 and M=50, respectively.

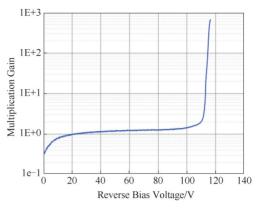

The photocurrent multiplication gain defined through equation (1) is shown in Fig. 3. In the following formula,  $I_{\rm light}$  represents the total current,  $I_{\rm ph}$  denotes the photocurrent, V represents the reverse bias voltage and  $V_0$  stands for the reference reverse bias voltage for  $M=1^{[15]}$ .  $V_0=20$  V was used for the data shown in Fig. 3. The test result indicates that the reverse bias voltage of the device is about 114 V at the typical photocurrent multiplication gain M=50. Besides, the photocurrent multiplication gain is up to 100 at reverse bias voltage of 114.5 V.

$$M = \frac{I_{\rm ph} \left( V \right)}{I_{\rm ph} \left( V_0 \right)} = \frac{I_{\rm light} \left( V \right) - I_{\rm dark} \left( V \right)}{I_{\rm light} \left( V_0 \right) - I_{\rm dark} \left( V_0 \right)} \qquad , \quad (1)$$

### 2. 2 Responsivity

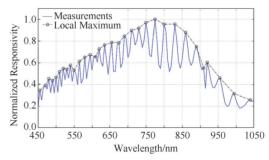

The normalized spectral responsivity for the lateral linear mode APD is obtained at the low bias voltage of 20 V with unity gain (M=1) with the spectral responsivity test system and is shown in Fig. 4. The normalized responsive wavelength range of the device is tested to be  $450\sim1050$  nm. The maximum responsivity wavelength of

Fig. 1 Schematic views of APD (a) cross section, (b) simplified electric field distribution, (c) the microscopic picture of the complete APD device, (d) the microscopic picture of the photosensitive region (Unit: µm)

图1 APD示意图(a)横截面,(b)电场分布,(c)APD器件的显微照片,(d)光敏区的显微照片(单位: μm)

Fig. 2 Currents vs. reverse bias voltage 图 2 电流-反向偏置电压特性

the device is about 775 nm at 20 V while M=1. With unity gain (M=1), the responsivity at 532 nm is about half of the maximum. As shown in Fig. 4, the spectral response curve reveals peak of interference with wave-

Fig. 3 Multiplication gain vs. reverse bias voltage 图 3 增益-反向偏置电压特性

length, which is caused by the multi passivation layers through 0.35  $\mu m$  high voltage CMOS process. A black broken line is marked by fitting peaks of measured data. It shows the definite trend relationship between responsivity and wavelength (450~1 050 nm) if an anti-reflective coating (ARC) layer is fabricated through 0.35  $\mu m$  high voltage CMOS process in the future.

Fig. 4 Normalized responsivity vs. wavelength (450 ~ 1050 nm)

图 4 归一化响应-波长特性

## 3 Conclusions

The lateral linear mode avalanche photodiode with the photo sensitive area of 618  $\mu$ m² is implemented through 0.35  $\mu$ m high voltage CMOS process. The lateral SACM and DNTUB/DPTUB/Pi/SPTUB layers are adopted. The breakdown voltage is observed about 114.7 V. And the dark currents are tested to be about 15 nA and 66 nA at gain M=10 and M=50, respectively. The responsive wavelength range is 450 ~ 1050 nm. The maximum responsivity wavelength is about 775 nm at 20 V while M=1. With improved anti-reflective coatings (ARC), the spectral response of the device is expected to be better.

#### References

- [1] Christensen O. Quantum efficiency of the internal photoelectric effect in silicon and germanium [J]. *Journal of Applied Physics*, 1976, 47 (2):689-695

- [2] Seeger K. Impact ionization and avalanche breakdown [M]. Semiconductor Physics. Berlin, Heidelberg; Springer Berlin Heidelberg. 1982:291-301.

- [3] Cheng Z, Xu H, Chen Y. Design of low noise avalanche photodiode single element detectors and linear arrays through CMOS process [C]. Proceedings of the Proc SPIE, Advanced Photon Counting Techniques XIII, F, 2019.

- [4] Wegrzecka I, Wegrzecki M, Grynglas M, et al. Design and properties of silicon avalanche photodiodes [J]. Opto-Electron Rev, 2004, 12(1):95-104.

- [5] Brandl P, Jukic T, Enne R, et al. Optical wireless and receiver with high background-light immunity for increased communication Distances [J]. IEEE Journal of Solid-State Circuits, 2016, 51 (7): 1663-1673.

- [6] Brandl P, Enne R, Jukic T, et al. OWC using a fully integrated optical receiver with large-diameter APD[J]. IEEE Photonics Technology Letters, 2015, 27(5):482-485.

- [7] Enne R, Steindl B, Zimmermann H, et al. Improvement of CMOS— Integrated vertical APDs by applying lateral well modulation [J]. Photonics Technology Letters, IEEE, 2015, 27(18):1907–1910.

- [8] Enne R, Steindl B, Zimmermann H. Speed optimized linear-mode high-voltage CMOS avalanche photodiodes with high responsivity [J]. Optics Letters, 2015, 40(19):4400-4403.

- [9] Takai I, Matsubara H, Soga M, et al. Single-photon avalanche diode with enhanced NIR-sensitivity for automotive LIDAR systems [J]. Sensors (Basel), 2016, 16(4):459.

- [10] Iiyama K, Takamatsu H, Maruyama T. Silicon lateral avalanche photodiodes fabricated by standard 0.18 µm CMOS process [C]. 2009 35th European Conference on Optical Communication, 2009:1-2.

- [11] Tseng C K, Chen K H, Chen W T, et al. A high-speed and low-breakdown-voltage silicon avalanche photodetector [J]. IEEE Photonics Technology Letters, 2014, 26(6):591-594.

- [12] Cifteioglu B, Zhang J, Zhang L, et al. 3-GHz Silicon Photodiodes Integrated in a 0.18-\(\mu\mathrm{m}\) CMOS Technology [J]. Photonics Technology Letters, IEEE, 2008, 20(24):2069-2071.

- [13] Vilella E, Vilà A, Palacio F, et al. Characterization of linear-mode avalanche photodiodes in standard CMOS[J]. Procedia Engineering, 2014, 87:728-731.

- [14] Hsieh Y C, Chou F P, Wang C W, et al. 850-nm edge-illuminated si photodiodes fabricated with CMOS-MEMS technology [J]. IEEE Photonics Technology Letters, 2013, 25(20):2018-2021.

- [15] Ripoche G, Harari J. Avalanche photodiodes [J]. Optoelectronic sensors, 2009: 58-109.